# PFC + Stand By CM6807

85+

with

10 pin PFC/Stand By Combo

### **CM6807**

# Design process

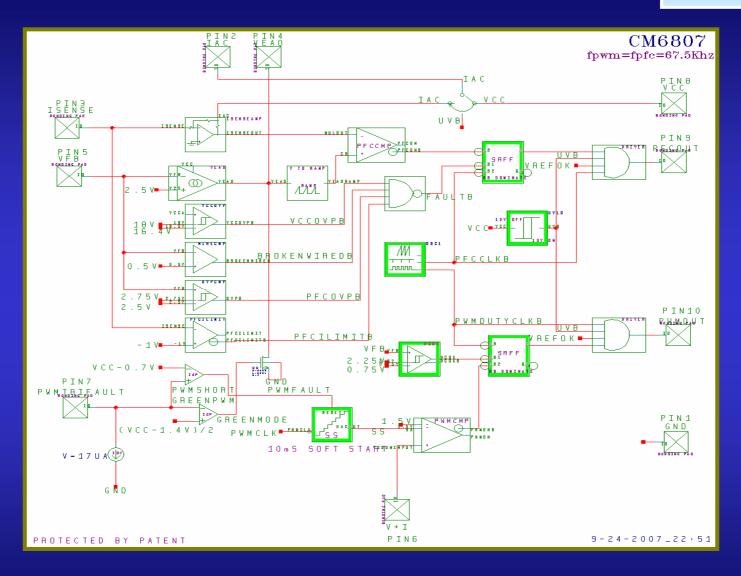

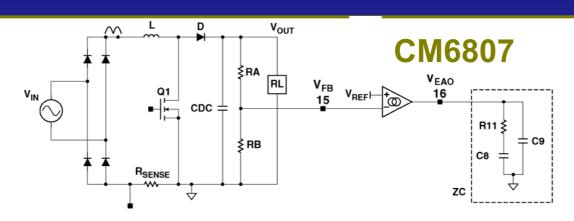

CM6807 Simplified Block Diagram

### **PFC Control:**

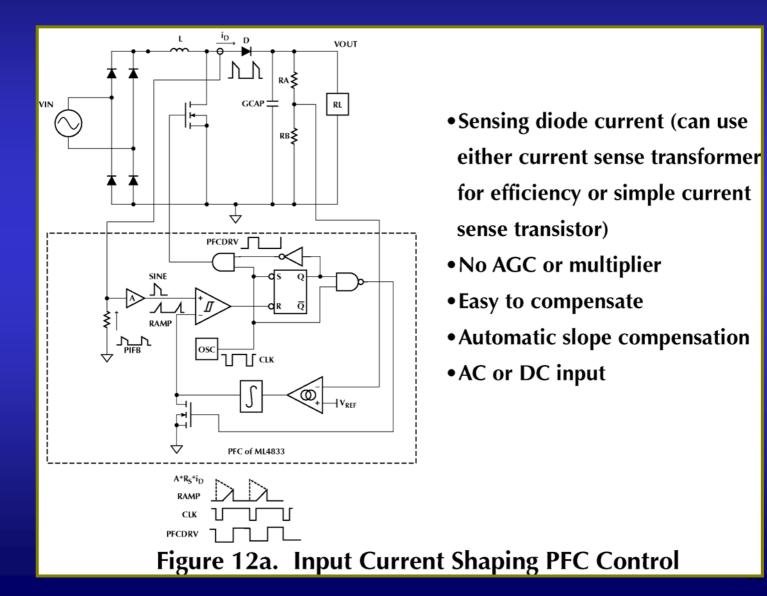

Leading Edge Modulation with Input Current Shaping Technique

(ICST)

•ICST is based on the following equations:

**PFC Control: ICST**

$$R_e = V_{in} / I_{in}$$

$$\bar{I}_l = I_{in}$$

(1)

- •Equation 2 means: average boost inductor current equals to input current.

- •Assume that input instantaneous power is about to equal to the output instantaneous power.

$$\therefore V_{in} \times \overline{I}_{l} \approx V_{out} \times \overline{I}_{d}$$

$$V_{out} / V_{in} = 1 / (1 - d)$$

(3)

•For steady state and for the each phase angle, boost converter DC equation at continuous conduction mode is:

•Rearrange above equations, (1), (2),(3), and (4) in term of Vout and d, boost converter duty cycle and we can get average boost diode current equation (5):

$$\bar{I}_d = \frac{(1-d)^2 \times V_{out}}{R_e}$$

(5)

•Also, the average diode current can be expressed as:

$$\bar{I}_d = \frac{1}{T_{sw}} \int_0^{T_{off}} I_d(t) \cdot dt \tag{6}$$

•If the value of the boost inductor is large enough, we can assume

$$I_d(t) \sim I_d$$

I<sub>d</sub> is constant during each switching period, 1/67.5khz.

- •It means during each cycle or we can say during the sampling, the diode current is a constant.

- •Therefore, equation (6) becomes:

$$\bar{I}_d = \frac{I_d \times t_{off}}{T_{sw}} = I_d \times d' = I_d \times (1 - d)$$

<u>(7)</u>

$$I_{d} \times d' = \frac{(d')^{2} \times V_{out}}{R_{e}}$$

$$\therefore I_{d} = \frac{d' \times V_{out}}{R_{e}}$$

$$\therefore I_{d} = \frac{V_{out}}{R_{e}} \times \frac{t_{off}}{T_{sw}}$$

•Using this simple equation (8), we implement the PFC control section of the PFC-PWM controller, CM6805/6 & CM6903

(8)

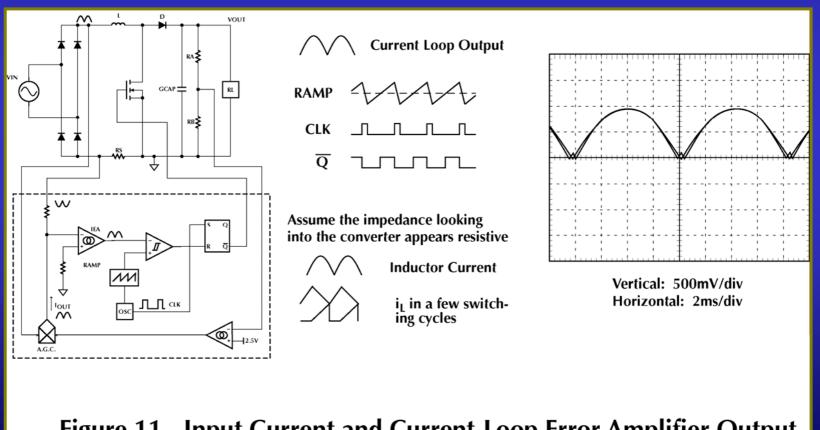

#### Review Leading Edge Modulation & Average Current Mode PFC Control

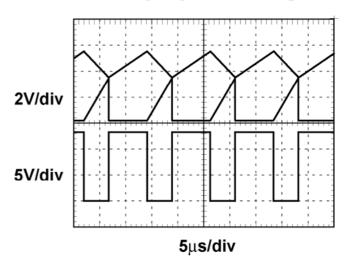

Figure 11. Input Current and Current-Loop Error Amplifier Output

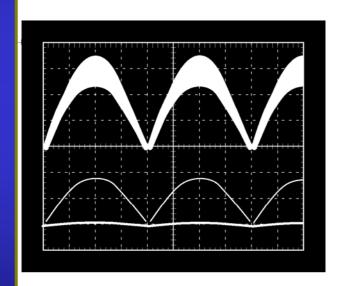

### **Experimental Results of 100W Boost Converter**

**Top Trace: Voltage Signal of**

Inductor Current Bottom Trace: RAMP

### **Duty Cycle Timing**

Top Trace: Voltage Signal of

Inductor Current Middle Trace: RAMP

**Bottom Trace: PFC Gate Drive**

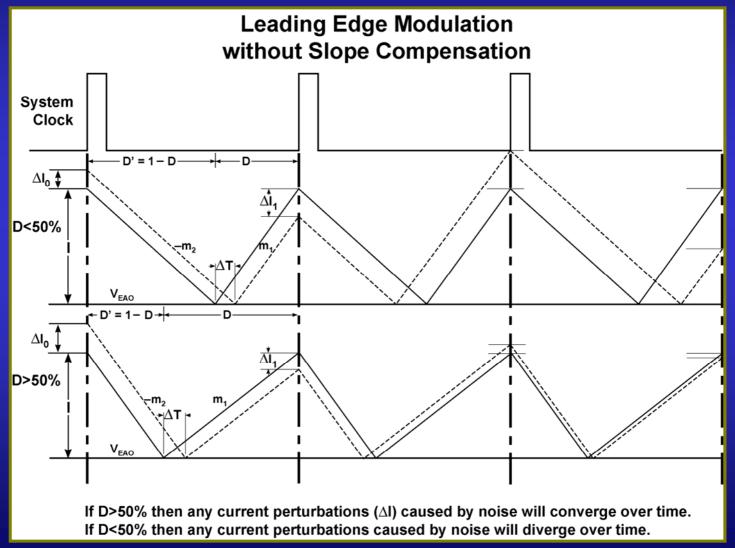

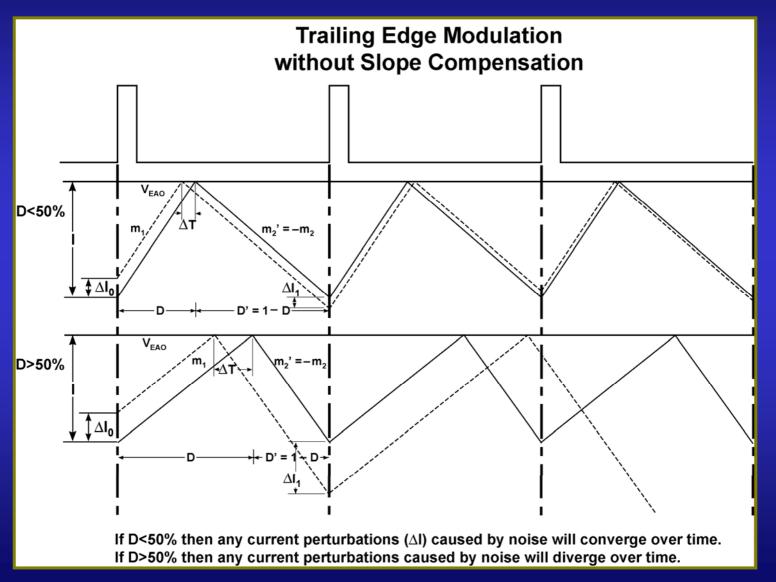

Leading edge modulation current-mode needs slope compensation when D (the duty cycle) < 0.5.

V<sub>EAO</sub> is the voltage error amplifier output; I is the inductor current; m<sub>1</sub> is the rising slope of the inductor current waveform; m<sub>2</sub> is the falling slope of the inductor current waveform.

The following equations can be derived:

$$\Delta T = \frac{\Delta I_0}{m_2} \tag{1}$$

$$\Delta T = \frac{\Delta I_1}{m_1} \tag{2}$$

(1) and (2) yield (3):

$$\Delta I_1 = -\Delta I_0 \times \frac{m_1}{m_2} \quad (3)$$

In general form:

$$\Delta I_n = \left(-\Delta I_0 \times \frac{m_1}{m_2}\right)^n \quad (4)$$

$$D' = 1 - D \tag{5}$$

$$I = m_2 \times D' \tag{6}$$

$$I = m_1 \times D \tag{7}$$

$$m_2 \times D' = m_1 \times D$$

(8)

So the relationship between D and  $\Delta I$  is:

$$\Delta I_n = \left(-\Delta I_0 \times \frac{D'}{D}\right)^n \qquad (9)$$

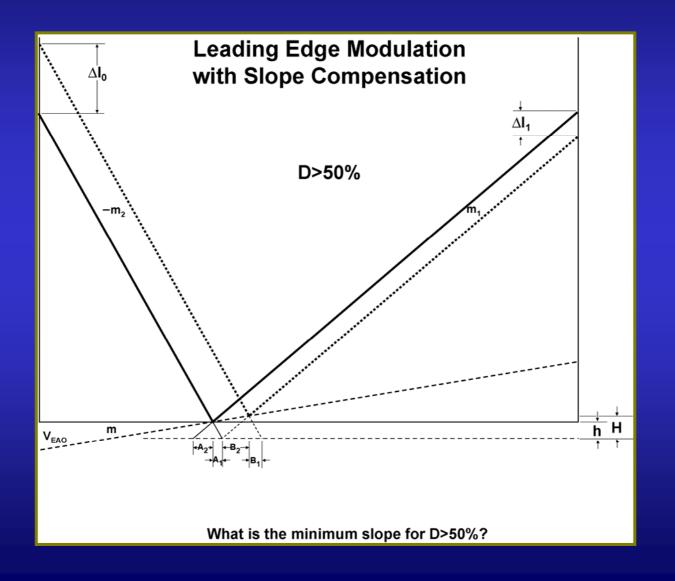

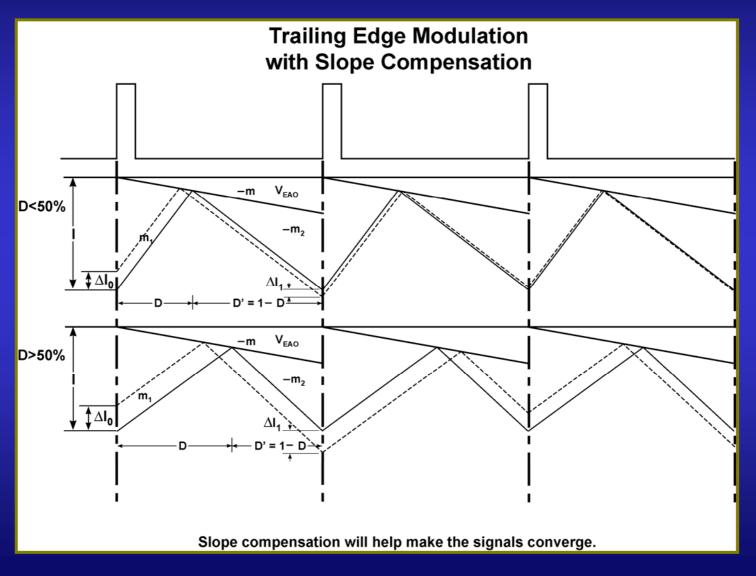

This leads to the conclusion that when the duty cycle (D) is greater than 50% for leading edge modulation without slope compensation the current loop is stable. And, when the duty cycle is less than 50%, the current loop is unstable.

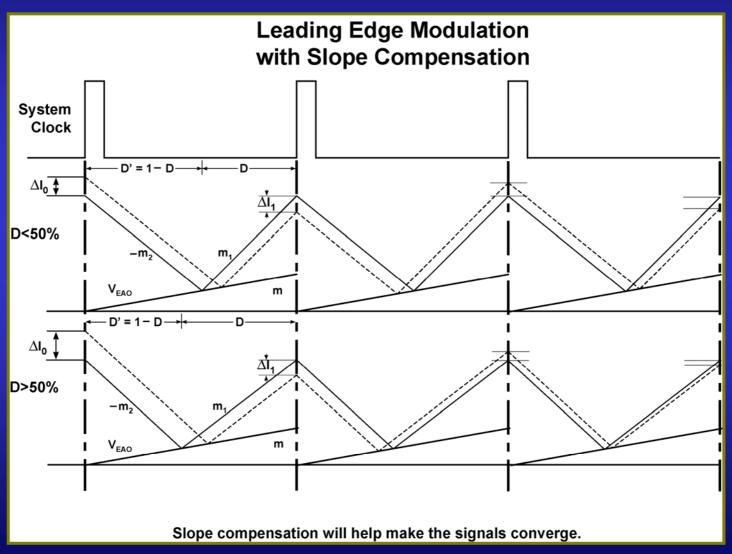

When a current-mode converter uses leading edge modulation with slope compensation the current loop is stable for all values of duty cycle.

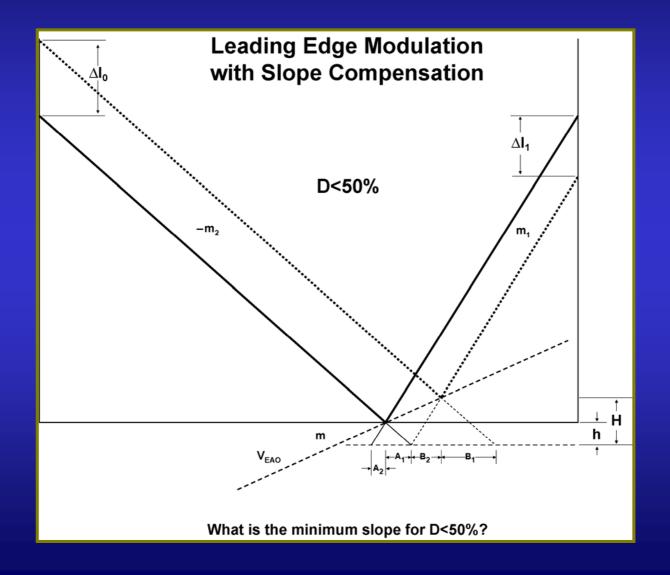

In the next set of equations A,  $A_1$ ,  $A_2$ , B,  $B_1$ ,  $B_2$ , H, and h are used for deriving the equations and have no physical properties.

$$A = \frac{\Delta I_1}{m_1}$$

$$A_1 = \frac{h}{m_2}$$

$$A_2 = \frac{h}{m_1}$$

$$B = \frac{\Delta I_0}{m_2}$$

$$B_1 = \frac{H}{m_2}$$

$$B_2 = \frac{H}{m_1}$$

$$A = A_1 + A_2$$

$B = B_1 + B_2$   $H - h = (A_1 + B_2) \times m$

From these the relationships among the inductor current slopes, the compensation slope, and the inductor current difference are:

$$\Delta I_1 = -\Delta I_0 \times \frac{(m_1 - m)}{(m_2 + m)}$$

(10)

For a stable current loop the following equations exist:

$$\frac{(m_1 - m)}{(m_2 + m)}$$

<1 (11)  $m > 0.5 \times m_1$  (12)

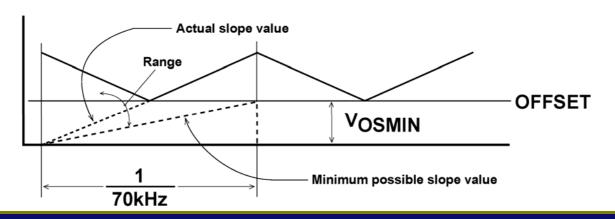

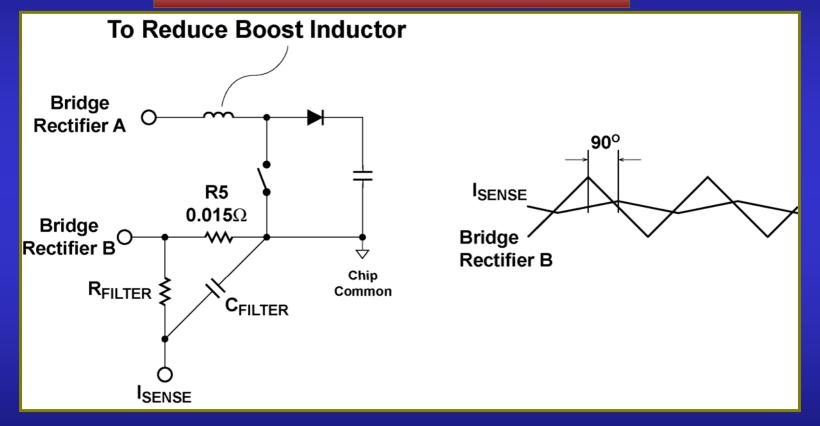

### PFC Current Mode Leading Edge Modulation:

When Duty Cycle is less than 50%, it needs the slope compensation.

Vos goes up <----> Ramp Slope goes up

The worst condition occurs when D = 0 and  $V_{\text{IN}} = 380$ V. At that time:

$$\frac{di_L}{dt} = \frac{V_{IN}}{L} = \frac{380}{L} \tag{1}$$

$$\frac{1}{S \times R_{Filter} \times C_{Filter} + 1} \times R5 \times \frac{di_{L}}{dt} = \frac{380}{L} \times R5 \times \frac{1}{S \times R_{Filter} \times C_{Filter} + 1}$$

(2)

$$\therefore V_{OSMIN} = \frac{380}{L} \times R5 \times \frac{1}{\sqrt{(R_{Filter} \times C_{Filter} \times 2\pi70 \text{kHz})^2 + 1^2}} \times \frac{1}{70 \text{kHz}}$$

(3)

**Champion Microelectronic**

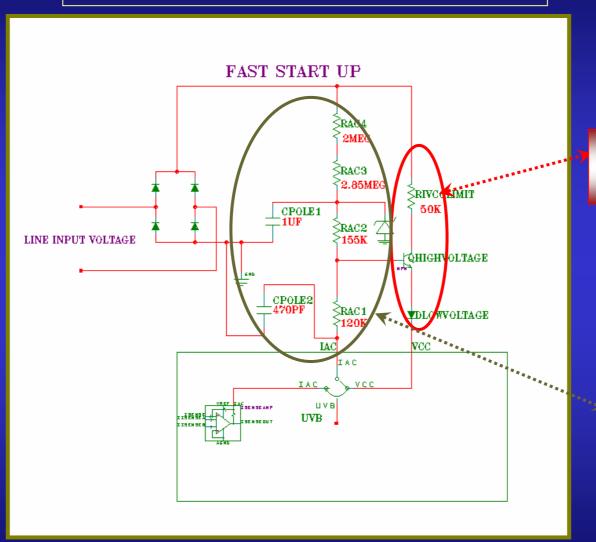

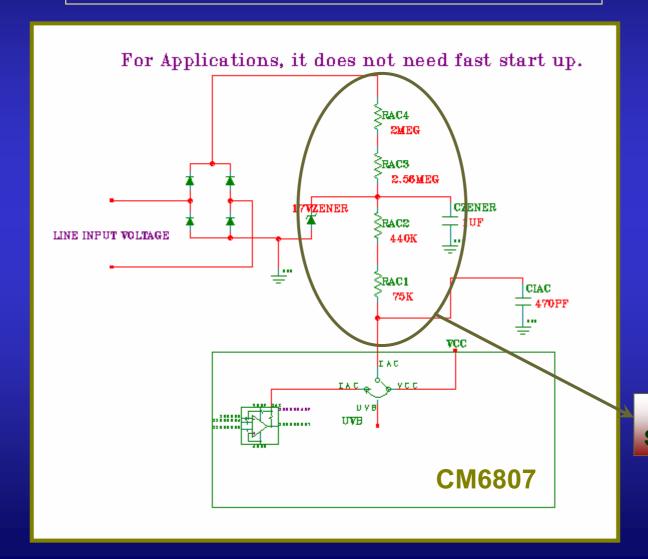

IAC, Pin 2: StartUp and PFC Slope Comp VCC, Pin 8 For fast start up applications

PFC + Stand By CM6807

**PFC Control: ICST**

Vcc Fast Start Up

cc start up typical~100uA

PFC Current Loop Slope Compensation

CM6807 IAC have the Switch to switch to VCC During start up

## IAC, Pin 2: StartUp and PFC Slope Comp VCC, Pin 8

PFC Current Loop

Slope Compensation

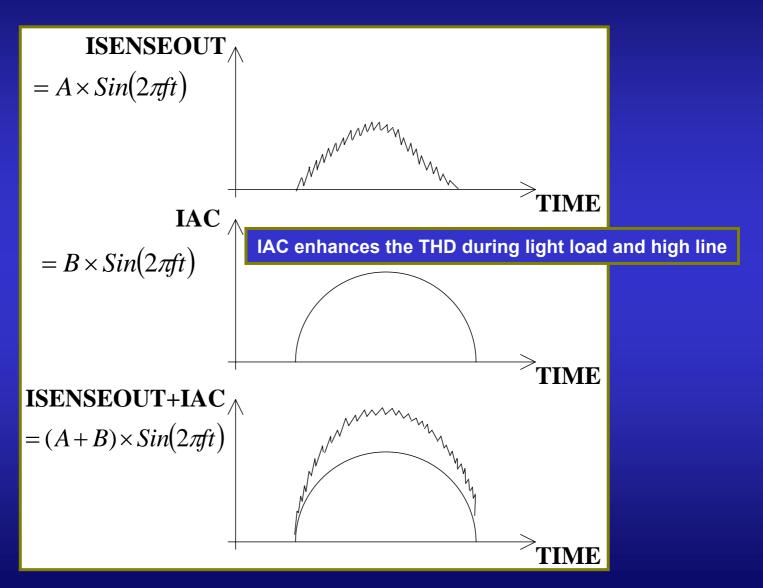

#### Isense, Pin 3

- 2 purposes to add Isense filter:

- Protect IC during inrush current

- Using smaller inductor and still having good THD

Usually, the pole of Isense filter ~ 1/6 of the switching frequency, and it is fsw/6 = 1/(2  $\times$   $\pi$   $\times$  R<sub>filter</sub> $\times$ C<sub>filter</sub>)

If R<sub>filter</sub> =1K  $\Omega$ , C<sub>filter</sub> =14.15nF.

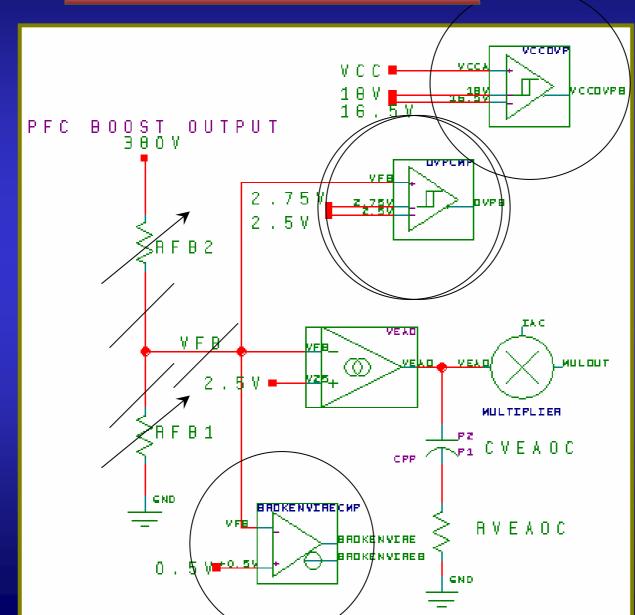

### Veao (pin4) and Vfb (pin5)

#### **PFC Control: ICST**

$$\therefore \frac{\Delta V_{OUT}}{\Delta V_{EAO}} = \frac{P_{IN AVERAGE}}{V_{OUT} \times \Delta V_{EAO} \times S \times C_{DC}}$$

(1)

$$\therefore \frac{\Delta V_{FB}}{\Delta V_{OUT}} = \frac{R_B}{R_A + R_B} = \frac{2.5V}{380V}$$

(2)

$$\therefore \frac{\Delta V_{EAO}}{\Delta V_{FB}} = Gm \times Z_{C}$$

(3)

$$\therefore \text{Loop Gain} = \frac{\Delta V_{\text{OUT}}}{\Delta V_{\text{EAO}}} \times \frac{\Delta V_{\text{FB}}}{\Delta V_{\text{OUT}}} \times \frac{\Delta V_{\text{EAO}}}{\Delta V_{\text{FB}}} = \frac{P_{\text{IN AVERAGE}} \times 2.5V}{V_{\text{OUT}} \times \Delta V_{\text{EAO}} \times S \times C_{\text{DC}} \times 380V} \times \text{Gm} \times Z_{\text{C}}$$

(4)

For CM6807,  $\triangle V_{EAO} \sim 6V - 0.7V = 5.3V$  Veao (pin4) and Vfb (pin5)

**PFC Control: ICST**

Easy to meet UL1950

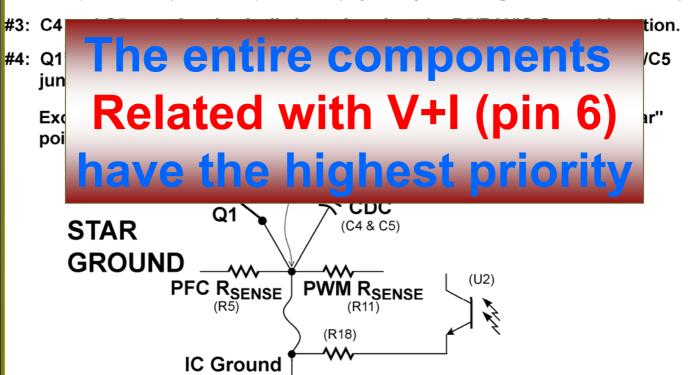

### GND (pin1)

### Layout Issues, in order of importance

- #1: R5 and R11 must be physically butted against one another, and their junction must be connected to the IC Ground pin. If there is switching current minimize the distance to chip gnd.

- #2: R18 (from the opto islator) must be physically butted against the IC Ground pin.

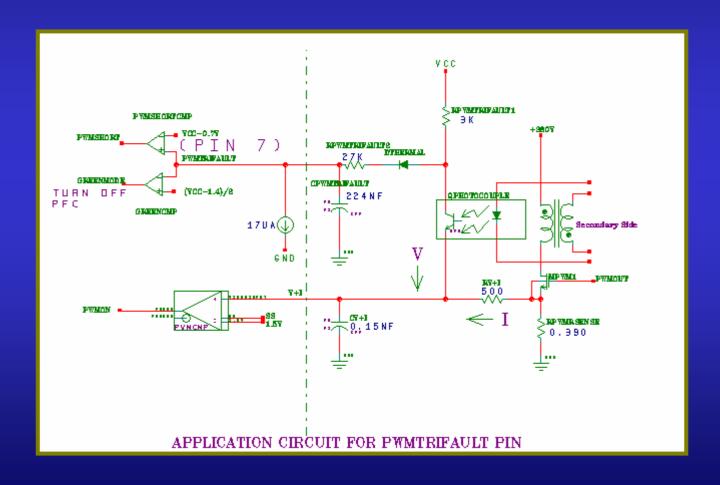

# V+I, (pin 6) and PWMtrifault, (pin 7) For FlyBack Converter

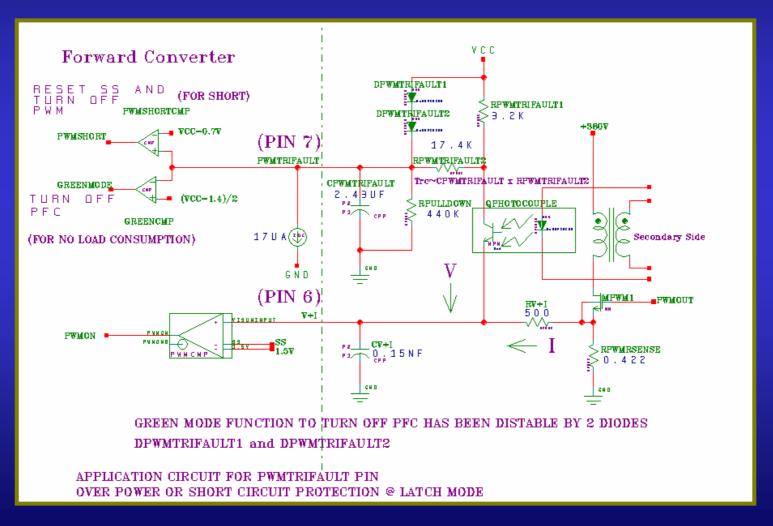

## V+I, (pin 6) and PWMtrifault, (pin 7) for Forward Converter

# CM6807 PFC + Stand By

For 85+ LCD TV or Desk Top